MOSFET Structure 반도체 공학이나 전자회로 카테고리에 대한 MOSFET에 대한 설명은 정말 많이 해왔는데 이번에는 기초보다는 더 응용된 내용을 다뤄보자.

MOSFET = Metal – Oxide – Semiconductor Field – Effect Transistor 앞에 metal ~ Semiconductor 는 구조를 field ~ transistor 는 성능을 의미한다 .

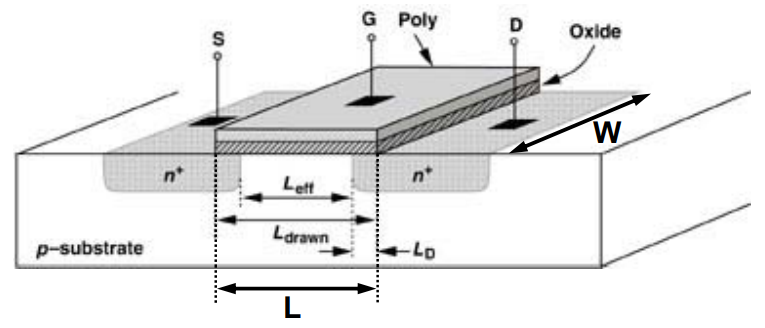

L=gate length : 공정 시 중요한 parameter이다. 5nm technology 공정에서 5nm이 의미하는 것이 이 L이다. Leff는 반도체공학 포스팅에서 설명했듯이 실제 채널이 형성되는 길이를 의미한다. 공정시 source나 drain 단이 gate length를 약간 침범할 수밖에 없는데, 그러한 점을 고려하여 제시한 것이다.

최근 공정에서 발생하고 있는 문제에 대해서 조금 알아보기로 한다.

gate voltage δV 에 의해 전기장(Electric Field)이 형성된다.-> 이때 L이 작아지면 VDS는 더 크게 작용한다. -> gate voltage VG가 크게 적용되면 transistor가 전류를 흐르거나 control이 가능하다. -> 그러기 위해서는 tox가 얇아야 한다.그렇지만 tox가 너무 얇으면 깨지기 쉽다.위와 같이 ① highk 물질을 사용하거나 ② VG가 작더라도 transistor가 ON 되어야 한다.(Vth가 작아야 한다)

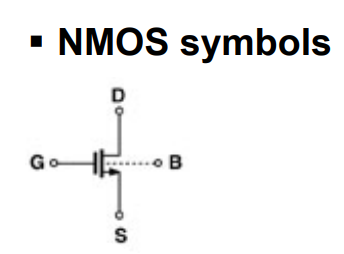

①highk 물질 사용 gate length L이 매우 작아졌고, tox도 점차 작아졌다. 그런데 oxide thickness(tox)가 너무 작으면 MOSFET의 구조에서 oxide가 제 역할을 못하게 된다. 그래서 highk 물질을 쓰게 된다. highk는 같은 L이라도 tox가 더 두꺼운 것을 의미한다. 「EOT」를 통해서 그 값을 계산해 물질을 평가하기도 한다. 자세한 내용은 아래 링크를 참조하기 바란다.원래는 물리전자공학을 전부 다루고 그에 대한 심화과정에서 봐야 하는데… 포스팅을 시작한 지 얼마 되지 않아 blog.naver.com ② VG를 작게 설계공정이 스케일링다운할수록 필요한 공급전압이 작아지고 소비전압도 작아진다.=> digital 회로에서는 좋지만 아날로그 회로에서는 나쁘다.Analog 회로에서는 SNR에 의해 성능을 결정한다.그러나 device noise는 줄일 수 없기 때문에, device signal이 크면 SNR이 좋아진다. 그런데 device signal을 키우기 위해서는 VG를 키워야 하는데, 그렇게 하면 tox가 깨질 수도 있기 때문에 signal을 크게 만들 수는 없다.그래서 요즘은 이러한 문제를 안고 digital 회로로 compensation을 해준다고 한다.NMOS와 PMOS symbol은 다음과 같다.

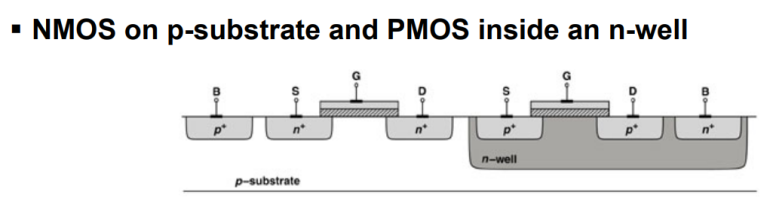

일반적으로 공정에서 NMOS를 p-s ubstrate 상에서 형성하게 된다. 그리고, p-substrate에 n-well을 형성하고, 그 위에 PMOS를 형성하게 된다. 다음 그림을 참고하면 된다.

이러한 구조에서 NMOS의 모든 body는 모두 동일하게 연결된다. (VDD) 그런데 PMOS는 p-substrate 내에 존재하는 n-well의 body를 따로 접속 가능하다.MOS I/V Characteristics [Threshold Voltage]Vg가 Vt보다 커지면 channel이 형성되어 drain-source 간에 전류가 흐르게 된다.(subthreshold 등 다양한 물리적 이슈가 있는데 다음 포스팅에서 짧게 다루도록 하겠다.)

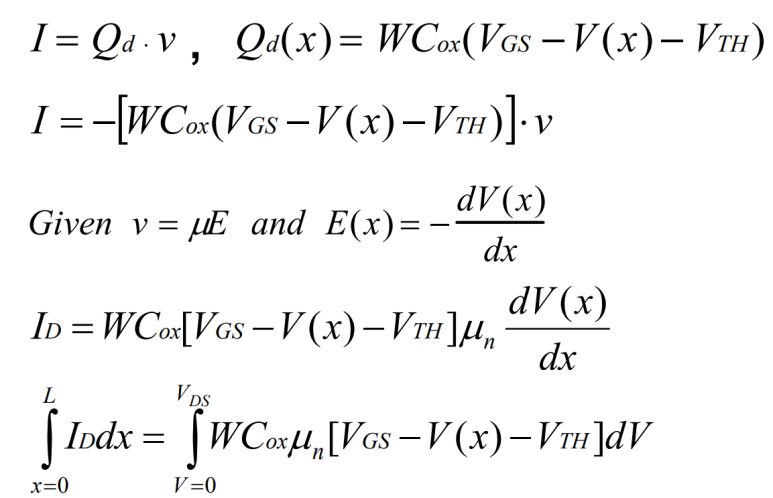

[ Derivation of I/V Characteristics ]

Biascondition에서의 volta ge 조건은 MOSFET가 saturation region으로 동작할 수 있도록 하는 것이다.

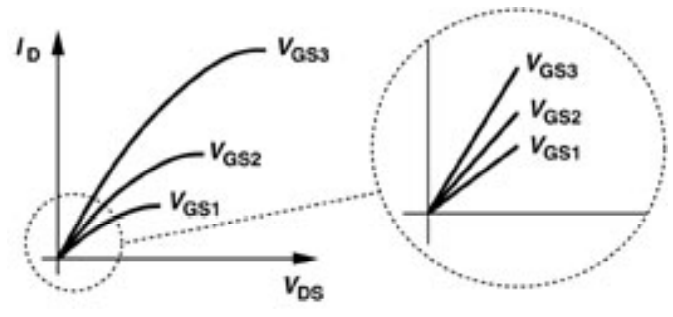

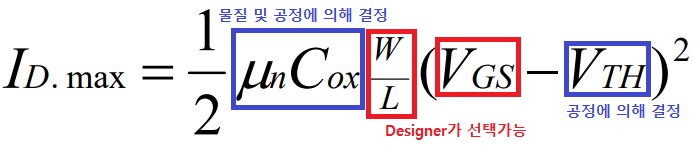

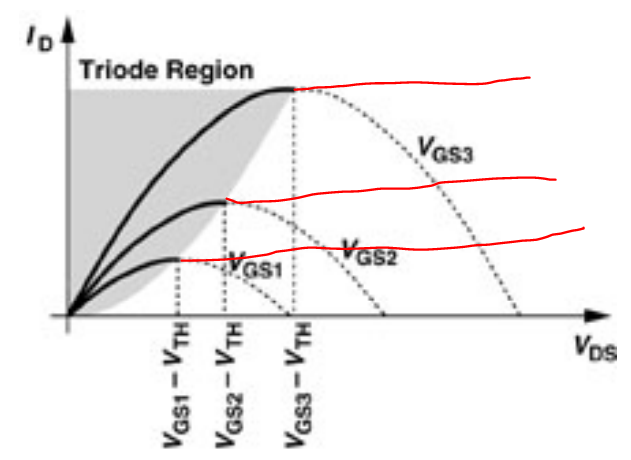

Saturation region에서는 VDS가 커져도 더 이상 전류 ID가 증가하지 않는다.즉 VGS-VTH=VDS일 때 pinch-off가 발생하고 그 때의 전류값이 최대전류값이 된다.

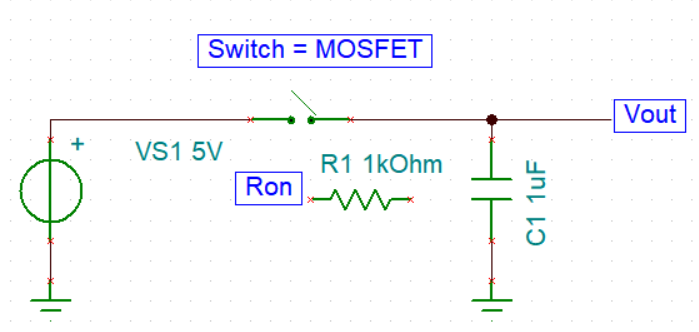

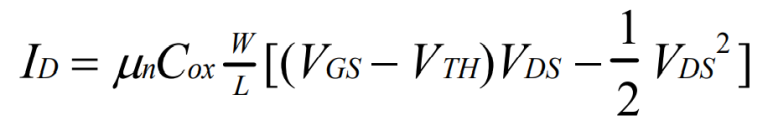

*변경할 수 있는 옵션이 많을수록 설계하는데 더욱 어려워진다.Cox는 단위면적당 capacitance를 의미하는데 유전율 ε은 물질에 의해 결정되며 간격 d는 공정에 의해 결정된다. W/L은 aspectratio에서 MOSFET의 width와 length를 의미한다.[Triode Region] Triode Region에서 동작하는 MOSFET은 주로 switch로 이용된다.

이 영역(VDS<2(VGS-VT H))에서는, MOSFET가 마치 저항과 같이 동작한다.

예를 들어 다음과 같은 회로가 있다고 생각해 보자.

Tina Tool을 사용한 회로는 L PF로 동작하는 회로로 주파수가 낮을 때만 신호가 잘 전달된다.

Vout을 수식으로 나타내면 다음과 같다.이 때 대역폭을 정하는 pole 값은 1/RC이다.속도 향상을 위해 보다 큰 대역폭을 사용하는 것이 좋기 때문에 1/RC가 커야 한다.그러면 R값 또는 C값을 좀 더 작게 해야 되는데요.

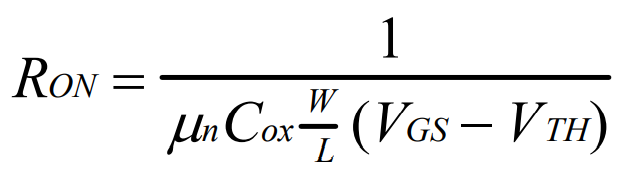

Capacitance를 줄이면 스위치에 의한 noisek T/C식으로 noise가 커진다. 따라서 C값은 더 이상 줄일 수 없다.여기에서는 R값을 줄여 보다 큰 대역폭을 갖게 할 필요가 있다.RON은 위와 같이 W/L, VGS 등과 같은 parameter에 의해 정해지는데 먼저 전류를 더 올려야 하는 것과 거의 비슷하다.

[ Saturation Region ]

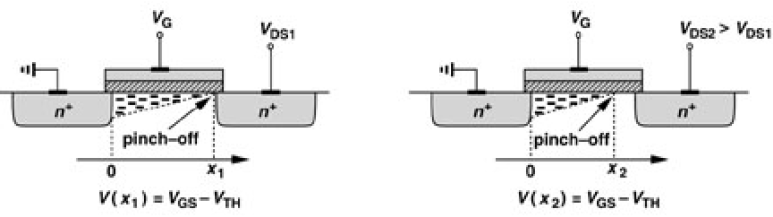

VDS가 커짐에 따라 채널이 형성되는데 channel은 Qox에 비례하여 증가한다. 전술한 바와 같이 VDS=VGS-VTH(where VGS>VTH)의 경우(pinch-off) 전류가 더 이상 증가하지 않는 saturation이 발생한다.

오른쪽 그림과 같이 VDS가 pinch-off일 때보다 커진다면 channel이 더 이상 형성되지 않고 drain 영역과 채널 사이의 빈 공간이 생기게 된다. 채널의 길이는 조금 짧아졌지만 channel charge의 양은 일정하게 유지되므로 전류가 saturtaion 된다. darin과 채널 사이의 빈 공간은 electric field에 의해 carrier가 이동하여 전류가 그대로 흐르게 된다.[ Transconductance gm ]

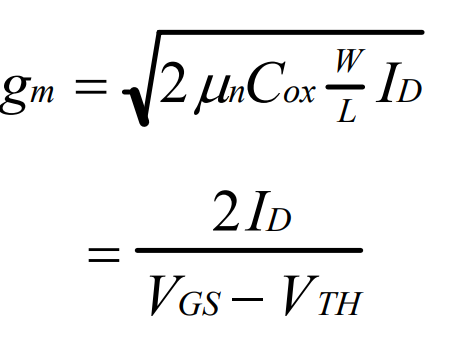

gm은 매우 중요한 paramet er이며, 반드시 기억해야 한다.

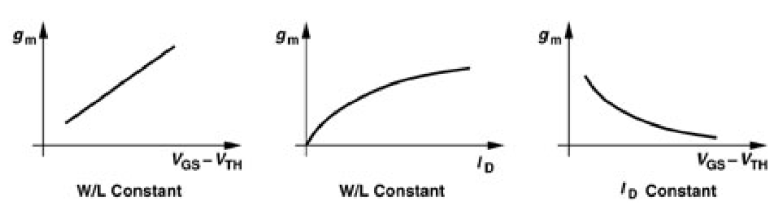

- W/L을 고정시켜 VGS가 커질수록 gm도 linear로 커지고 ID는 square로 커진다.2. W/L을 고정하고 ID가 커질수록 gm은 logarithm으로 커진다.3.ID를 고정하고, VGS가 커질수록 gm은 분수 함수의 형태로 감소하게 된다.

- 모두 위의 식으로부터 얻을 수 있는 그래프이다. 이러한 그래프의 개형을 아는 것은 이후에 우리가 회로를 설계할 때 gm의 optimum point를 찾거나 변화시킬 때 활용할 수 있다.